如何理解寄存器?

寄存器是嵌入式系统中最基础、也最容易被误解的概念之一。许多初学者觉得“操作寄存器”很神秘,仿佛在直接操控硬件的“神经”。其实,寄存器不过是 CPU 与外设之间通信的接口,是硬件行为的控制开关。

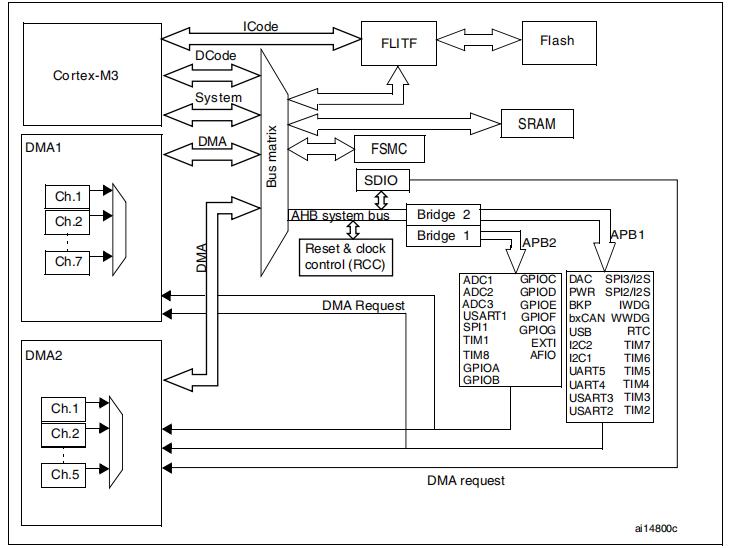

本文将从 冯·诺伊曼体系结构 出发,结合 STM32F10x 的系统框图,解析 ARM 与 ST 的分工,并深入讲解 外设寄存器的地址映射机制,带你彻底理解:寄存器到底是什么?它是如何工作的?

一、从冯·诺伊曼架构理解寄存器

要理解寄存器,必须回到现代计算机的基石—冯·诺伊曼体系结构(Von Neumann Architecture)。

该架构将计算机分为五个基本部分:

- 运算器

- 控制器

- 存储器

- 输入设备

- 输出设备

其中,运算器和控制器合称为中央处理器(CPU),而寄存器就位于 CPU 内部,是系统中最快的存储单元。

寄存器的本质

- 位置:位于 CPU 内部,速度远高于内存。

- 作用:暂存指令、地址、数据,参与运算和控制流程。

- 类比:如果把内存比作“仓库”,寄存器就是 CPU 手边的“工作台”——所有操作都必须在这里完成。

在嵌入式系统中,除了 CPU 内部的通用寄存器(如 R0-R15),还有一类特殊的寄存器:外设寄存器。它们虽然不位于 CPU 内部,但通过 内存映射 I/O(Memory-Mapped I/O) 被映射到系统的地址空间中,CPU 可以像访问内存一样读写它们。

✅ 所以,寄存器 = CPU 内部的工作单元 + 外设的控制接口

二、STM32F10x 系统框图:寄存器的物理位置

在深入代码之前,我们先看一张关键的图—STM32F10x 的系统架构图。

🧩 架构解析

这张图揭示了 STM32F10x 的核心通信路径与模块连接方式:

1. Cortex-M3 核心

- 位于左上角,是整个芯片的“大脑”。

- 包含通用寄存器(R0-R15)、程序计数器(PC)、堆栈指针(SP)等。

- 通过三条总线与外部通信:

- ICode:取指令

- DCode:访问数据(如常量)

- System Bus:访问外设和内存

2. 总线矩阵(Bus Matrix)

- 中央枢纽,协调多个主设备(CPU、DMA)对共享资源的访问。

- 支持优先级仲裁,确保关键任务不被阻塞。

3. AHB 系统总线

- 连接高速外设(如 Flash、SRAM、FSMC、SDIO)。

- CPU 和 DMA 都可以通过 AHB 访问这些资源。

4. APB1 / APB2 总线

- APB1(低速):连接 ADC、TIM2~7、UART2~3、I2C、SPI2/3 等。

- APB2(高速):连接 GPIOA-F、USART1、SPI1、TIM1、ADC1 等。

- 所有外设都通过这两个总线接入系统。

5. DMA 控制器

- DMA1 和 DMA2 可独立传输数据,减轻 CPU 负担。

- 例如:ADC 数据可直接传入 SRAM,无需 CPU 干预。

6. 外设模块

- 每个外设(如 GPIOA、USART1)都有自己的控制寄存器组。

- 这些寄存器通过 APB1/APB2 总线连接到 AHB,并映射到特定的内存地址。

🎯 寄存器在哪里?

以 GPIOA 为例:

- 在图中,GPIOA 位于 APB2 总线上。

- 它的寄存器组通过 Bridge 1 连接到 AHB 系统总线。

- CPU 通过 AHB → APB2 → GPIOA 的路径访问其寄存器。

💡 关键点:

外设寄存器虽然物理上在 GPIO 模块内,但逻辑上被映射到系统的内存空间中,因此可以像读写内存一样操作它们。

三、ARM 与 ST 的分工:谁定义了寄存器?

在 STM32 中,寄存器的设计涉及两个关键角色:ARM 和 ST(意法半导体)。

| 角色 | 职责 |

|---|---|

| ARM | 设计 CPU 核心(Cortex-M3) • 定义 CPU 内部寄存器(如 R0-R15、SP、LR、PC) • 定义系统控制寄存器(NVIC、SysTick、MPU 等) • 提供 CMSIS(Cortex Microcontroller Software Interface Standard)标准 |

| ST | 设计外设和芯片集成 • 定义 GPIO、USART、TIM 等外设的寄存器 • 确定外设寄存器的地址映射 • 提供 HAL 库、LL 库和参考手册 |

举例说明:

R0-R15、SP、PC:由 ARM 定义,所有 Cortex-M 芯片通用。GPIOx_MODER、USARTx_BRR:由 ST 定义,属于 STM32F10x 特有。NVIC_ISER(中断使能寄存器):由 ARM 定义,通过 CMSIS 访问。

✅ 总结:

- CPU 寄存器 → ARM 定义

- 外设寄存器 → ST 定义

- CMSIS 是桥梁,统一了对 Cortex 核心的访问方式。

四、STM32F10x 外设的地址空间:寄存器是如何被访问的?

STM32F10x 使用统一编址(Unified Addressing),所有外设寄存器都被映射到 4GB 的线性地址空间中。

STM32F10x 存储器映射(简化)

| 地址范围 | 区域 | 说明 |

|---|---|---|

0x0000 0000 – 0x1FFF FFFF |

Code / SRAM | 程序存储与内存 |

0x2000 0000 – 0x3FFF FFFF |

SRAM | 主内存 |

0x4000 0000 – 0x5FFF FFFF |

Peripheral | 外设寄存器区 |

0x6000 0000 – 0x9FFF FFFF |

FSMC | 外部存储控制器 |

0xA000 0000 – 0xDFFF FFFF |

保留 | |

0xE000 0000 – 0xFFFF FFFF |

Cortex-M3 内部外设 | NVIC、SysTick、DWT 等 |

注意:外设寄存器区(

0x4000 0000起)是理解寄存器访问的核心。

外设寄存器的具体映射(以 GPIOA 为例)

- 基地址:

0x4001 0800 - 寄存器偏移:

GPIOA_MODER(模式寄存器):+0x00→0x4001 0800GPIOA_OTYPER(输出类型):+0x04→0x4001 0804GPIOA_ODR(输出数据):+0x14→0x4001 0814

如何访问寄存器?

// 直接操作地址(寄存器映射)

#define GPIOA_BASE 0x40010800

#define GPIOA_MODER (*(volatile uint32_t*)(GPIOA_BASE + 0x00))

#define GPIOA_ODR (*(volatile uint32_t*)(GPIOA_BASE + 0x14))

// 配置 PA0 为输出模式

GPIOA_MODER |= (1 << 0); // MODER0[1:0] = 01

// 输出高电平

GPIOA_ODR |= (1 << 0);

✅ 这就是“寄存器开发”的本质:通过地址访问外设的控制寄存器。

现代开发中,ST 提供了 标准外设库(SPL) 或 HAL/LL 库,封装了这些地址操作,但底层仍是寄存器访问。

总结:寄存器到底是什么?

| 层面 | 理解 |

|---|---|

| 架构层面 | 冯·诺伊曼中的“工作台”,CPU 的高速存储单元 |

| 硬件层面 | CPU 和外设中的控制单元,通过地址映射暴露给软件 |

| 软件层面 | 一段可读写的内存地址,写入特定值可控制硬件行为 |

| 本质 | 硬件与软件之间的接口 |

延伸思考

- 为什么寄存器要用

volatile修饰?

→ 防止编译器优化,确保每次读写都访问硬件(寄存器值可能被外设修改)。 - 为什么不同 STM32 型号的外设地址可能不同?

→ 芯片设计差异,但同类外设的寄存器偏移一致,便于移植。 - 使用 HAL 库是否就不用懂寄存器了?

→ 否。理解寄存器有助于调试、优化性能,并应对库未覆盖的底层场景。

结语

寄存器并不神秘。它是嵌入式开发的“第一性原理”——所有高级库和框架,最终都建立在对寄存器的操作之上。

从冯·诺伊曼架构到 STM32F10x 的系统框图,再到外设地址映射,理解寄存器的本质,就是理解计算机如何控制硬件。掌握这一点,是迈向嵌入式高手的必经之路。